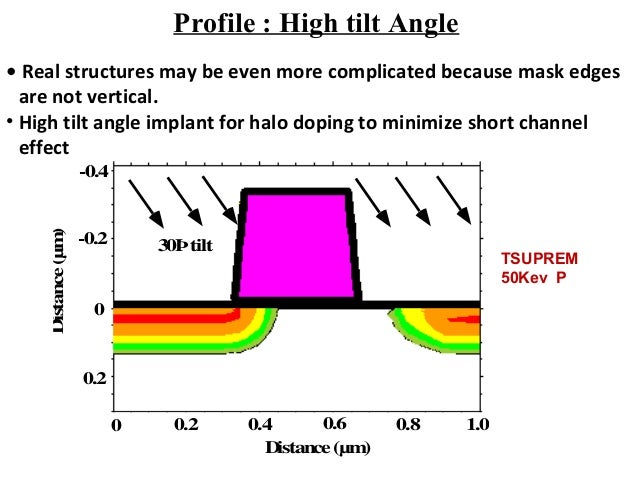

Results of Crystal-TRIM calculations for B implantations are compared with a comprehensive set of experimental data on range and damage profiles obtained by secondary ion mass spectroscopy, cross-sectional transmission electron microscopy, and channeling Rutherford backscattering spectroscopy. The other parameter is independent of temperature and models the onset of amorphization. One parameter describes the accumulation of amorphous pockets and depends on the target temperature. Using only two empirical parameters, the change of the shape of range distributions with growing dose as well as the formation of amorphous layers during ion bombardment can be simulated. The model is applied in the Crystal-TRIM code. If within a certain depth interval the density of amorphous pockets exceeds a critical value, abrupt amorphization occurs. The dynamic simulation of the formation of amorphous layers is described by an improved model. The statistical approach, which assumes the accumulation of amorphous pockets, is found to be the most realistic model for doses below the amorphization threshold. In addition, the reliability of VIISta 3000 from defect control perspective relevant to advanced device geometries is discussed.Ī critical review is given on phenomenological models of damage accumulation used in binary collision (BC) computer simulations of the dose dependence of the shape of as-implanted profiles and of the interdependence of channeling and damage buildup. The angle control and beam parallelism are demonstrated with implants over a wide energy range and for dopant applications such as well and halo implants. In this paper we discuss the performance characteristics of VSEA's VIISta 3000, single-wafer parallel beam, high-energy ion implanter. However, the zero degree implants require a tight control of beam angles and parallelism to ensure consistent device performance across the wafer. This transition is fueled by the necessity to eliminate limitations imposed by shadowing and encroachment effects stemming fro the thick photoresist mask, inherent to traditional off-axis we implants. In order to enable the high packing density and reduced well-spacing, zero angle well implants are required. In the DRAM device, the standby current at a short propagation delay time (tPD) was reduced effectively due to the decrease in the Ioff and contact resistance for the cold-IIP case.Īs device geometries scale, there is an Increasing requirement for a tight control of all process parameters related to doping. The contact resistance was reduced by ∼6% of the RT-IIP. Additionally, the drain induced barrier lowering was improved, and the on-current improvement was attributed to reducing the contact resistance through the reduction of EOR defects. Threshold voltage roll-off and off current (Ioff) increment, which are caused by a reduction in the distance between the gate and contact, were improved compared with room temperature implantation (RT-IIP). A shallow dopant profile was formed by the suppression of transient enhanced diffusion (TED) due to the reduction of end-of-range (EOR) defects. By making use of the above reported phenomenon, PMOS transistor can be made shorter without running into manufacturing control problem, resulting in bigger I on but the penalty is that the I off will become significantly higher.In this paper, to suppress transient enhanced dopant diffusion and improve short channel effects, cold implantation (cold-IIP) was applied to contact PLUG implantation in P-channel metal oxide semiconductor field effect transistors (PMOSFETs). However, this approach will make the PMOS transistor very sensitive to the statistical variation in the gate electrode length during manufacturing. The on-current can be increased by using PMOS transistor with smaller mask gate length compared to the NMOS transistor. Since the hole mobility is smaller than the electron mobility in silicon, PMOS transistor tends to have smaller on-current ( I on) than NMOS transistor. The advantage of the cross-over of halo implants can be understood as follows. The phenomenon of the cross-over of halo implant is more readily observed in PMOS transistors compared to NMOS transistors because for the same mask gate length, the effective channel length of PMOS transistor tends to be smaller than that of NMOS transistor. This paper demonstrates that the halo implant from the drain side can cross-over to the source side and vice versa for the look-ahead transistor test structures (transistor test structures with gate length smaller than that of the target transistor).

The merging of halo implants from the drain side and the source side creates a maximum in the magnitude of the threshold voltage and thus a minimum in the off-current in the metal-oxide-semiconductor transistors.

0 kommentar(er)

0 kommentar(er)